摘要

高速数据采集和回放系统在很多领域都有着广泛的应用,如雷达系统、地震勘测、无损检测、航空遥测等。随着信息科学的飞速发展,高速数据采集和回放系统的数据处理任务变得越来越繁重,其对于数据存储的要求也越来越苛刻,需要既能支持数据的高速传输和非易失性存储,又拥有海量数据存储容量。

现有系统大多只具有单一的高速数据传输或非易失性海量数据存储功能,无法同时满足这些需求。

为了克服现有系统的不足,本文采用非易失性存储器FLASH组成的阵列作为数据存储器,设计了一个集成FLASH容错算法的高速数据采集回放系统。

通过对各个电路模块的有效控制,实现了高速数据采集和回放功能,同时可存;储海量数据。另外,针对FLASH在数据存储过程中因坏块而引起的数据丢失问题,本文在实现系统功能钓过程中提出一种FLASH容错算法,实现了对FLASH坏块的动态检测和管理,保证了数据存储的准确性与安全性。

本文主要工作如下:

1.介绍了系统硬件方案,设计了系统FPHA固件逻辑架构,分析了系统设计的三大技术难点,包括FLASH阵列模块与外围模块的交互设计、FLASH通用控制接口设计以及FLASH容错算法的设计及实现。

2.设计并实现了高速数据采集功能,包括高速ADC模块、FLASH阵列模块、USB3.0上传模块和采集模式下FLASH阵列模块与外围模块的交互。

3.设计并实现了高速数据回放功能,包括USB3.0下载模块、高速DAC模块和回放模式下FLASH阵列模块与外围模块的交互。

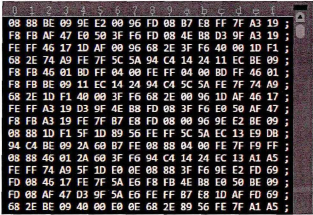

4.设计并实现了FLASH容错算法,包括FLASH坏块检测、逻辑一物理地址映射表的建立、动态更新和动态查询等功能。

5.搭建了系统的软硬件测试平台,并进行了大量测试实验,测试结果表明,系统实现了数据的高速采集、回放和非易失性海量存储等功能,FLASH容错算法有效解决了坏块管理问题。

关键词:数据采集,数据回放,FLASH, USB3.0, ADC, DAC

Abstract

High-speed data acquisition and playback systems are widely adopted in many fields, such as radar system; seismic survey, nondestructive testing, aviation telemetry and so on- With the rapid development of information technology, the data processing task of the high-speed data acquisition and playback system is becoming more and more arduous, thus further, leads to an increasing demand for data storage capacity Hence, it is necessary to develop a system with massive data storage capacity that supports high-speed data transmission supported and guarantees non-volatile storage demand guaranteed. Most of the existing systems only have a single high speed data transmission or non-volatile mass data storage function, which can not meet these requirements at_the same time.

In this thesis, FLASH chip arrays play a role一of data metnorizer and a high-speed data acquisition’ and playback system integrates with FLASH fault-tolerant algorithm is proposed to overcome the weakness of the existing systems. High-speed data acquisition and playback are accomplished with the effective control of each module and meanwhile it can store massive date. In addition, aiming at the problem of data loss caused by bad blocks of FLASH during data storage process, a FLASH fault-tolerant algorithm is also proposed, which realizes the detection and management of FLASH bad blocks and ensures the accuracy and security of data storageThe main work of this paper is organized as follows:

1. The hardware scheme of the system is introduced and the FPGA firmware architecture of the system is designed. Three major technical difficulties, namely the design of FLASH's fault-tolerant algorithm, the design of FLASH general control interface and the design of the interaction between FLASH Array and other modules are analyzed-2. The high-speed data acquisition function, including high speed ADC module, FLASH array, USB3.0 uploading module and interaction between FLASH array and other modules in acquisition mode, are well-designed and implemented.

3一The high-speed data playback function, including USB3.0 downloading module, high-speed DAC module and interaction between FLASH array and other modules in playback mode, are also designed and implemented.

4. The FLASH fault-tolerant algorithm, including the functions of FLASH's bad blocks detection, logical-physical address mapping table, dynamic updating and dynamic querying, are presented and implemented.

5. A software and hardware test platform is built, and a lot of test experiments are carried out- The test results show that the system realizes the functions of high speed acquisition, playback and nonvolatile mass storage of data. FLASH fault-tolerant algorithm effectively solves the problem of bad block management.

Keywords: Data acquisition, Data playback, FLASH, USB3.0; ADC, DAC

数据采集是指通过模数转换器(ADC)将温度、压力、流量、位移等模拟量采集转换成数字量后,再发送给上位机进行处理和分析的过程。而数据回放是指将存储在上位机中的数字信号通过数模转换器(DAC)转换为模拟信号并输出,是数据采集的逆过程数据采集和回放技术在很多领域都有着广泛的应用,如雷达系统、地震勘测、无损检测、航空遥测等。以雷达系统为例,由于现代雷达信号波形和信号处理过程越来越复杂,只有对实际环境下的雷达目标回波信号有深入的了解,才能保证信号处理方法的准确性和可靠性。在现代雷达系统设计中,广泛采用数据采集系统对回波信号进行采集和存储,并通过数据传输总线把采样数据上传到数据处理中心,利用信号处理算法进行进一步的分析和研究。另一方面,为了对雷达设备进行调试及性能评估,需要进行外场测试,也就是为雷达设备提供真实的场景。但是进行外场测试需要耗费巨大的人力、物力和财力,甚至有时这种条件是难以实现的。如果每次调试都进行外场测试,那耗费的资源将难以想象。此时,我们可以采用另一种方式,即将真实环境中的海量测量数据下载到数据回放系统中。在设备调试时,通过数据回放系统给雷达系统提供测试数据,从而达到模拟真实场景的效果。该方式还可以无限次数地进行、模拟,大大降低了调试雷达设备的成本,提高了调试的效率。因此,数据采集和回放系统已成为雷达领域中不可或缺的一部分。

在雷达系统、地震勘测、无损检测、航空遥测等领域中,现场信号具有重要作用。以雷达信号为代表的现场信号具有实时性强、数据速率高、数据量庞大和处理复杂等特点,这就对数据采集和回放系统提出了更高的要求,它不但需对上述现场信号进行高速、高精度的采样和回放,以便于后续对信号的完整复现和分析,同时还要拥有海量数据存储容量。另外,很多实验场合下,系统都着眼于保存现场数据,进而对数据进行离线处理。在利用数据回放功能模拟真实场景时,也需事先将海量实验数据下载到系统中存储,在需要时进行数据回放。因此,要求系统能对数据进行非易失性存储,即掉电后数据不丢失。

基于上述背景,本文设计了一个同时具有海量数据存储容量和非易失性存储功能的高速数据采集回放系统。系统既可以对外部模拟信号进行高速采集和海量存储,通过数据传输总线把采集数据上传到数据处理中心,也可以将回放数据下载到系统上,利用高速数据回放功能为外部系统提供测试数据,模拟真实场景。本系统可适用于雷达系统、地震勘测、无损检测和航空遥测等多个领域,具有广泛的应用前景。

本文采用FLASH阵列作为存储器,设计了一个集成FLASH容错算法的高速数据采集回放系统。一方面,在确保系统拥有海量数据存储容量和非易失性存储功能的前提下,实现了系统的高速数据采集功能和高速数据回放功能。系统有采集和回放两种模式。采集模式下,通过高速ADC模块采集外部模拟信号,并把诲量数据存储到FLASH阵列中。上传数据时,从FLASH阵列中读取数据,通过USB3.0接口将数据上传到上位机。回放模式下,上位机通过USB3.0接口把海量回放数据下载到FLASH阵列中。数据回放时,从FLASH阵列中读取数据,通过高速DAC模块回放出模拟信号。

另一方面,针对FLASH在数据存储过程中因坏块而引起的数据丢失问题,本文在实现系统功能的过程中提出一种FLASH容错算法,实现了对FLASH坏块的动态检测和管理,保证了数据存储的准确性与安全性。

最后,针对系统的功能和指标,搭建了系统的软硬件测试平台,对系统的高速数据采集功能、高速数据回放功能和FLASH容错算法的有效性分别进行了测试,测试结果验证了系统方案设计的合理性和容错算法的有效性,满足了系统的功能和指标要求。

高速数据采集回放系统开发:

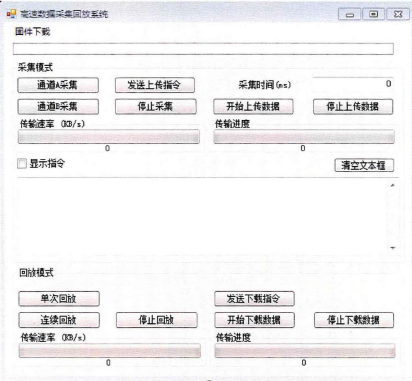

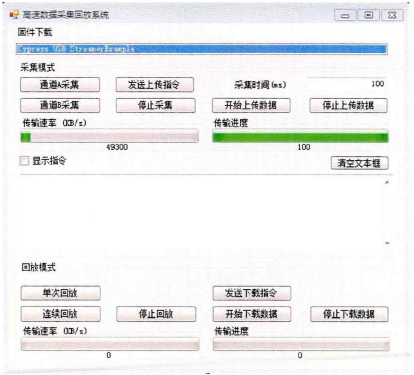

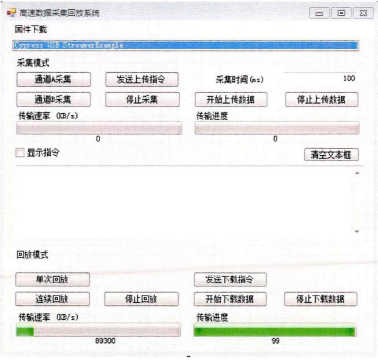

上位机人机交互界面

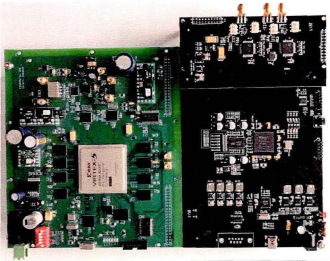

高速数据采集回放硬件电路板

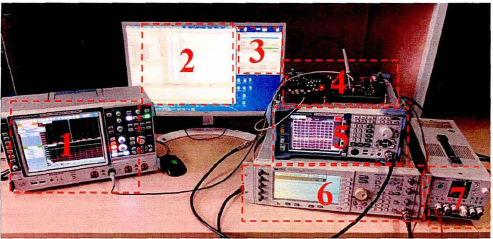

系统整体测试平台

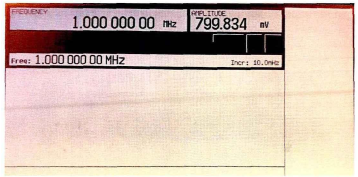

信号源输出1MHz正弦信号

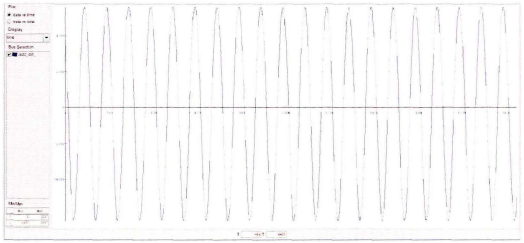

ChipScope捕获的1MHz正弦波波形

USB3.0数据上传过程

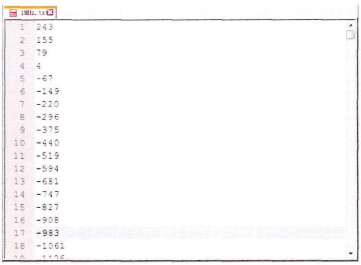

上位机接收到的数据

USB3.0数据下载过程

原始回放数据

目录

摘要

Abstract

目录

1 绪论

1.1 研究背景和意义

1.2 国内外研究现状

1.3 本文主要工作

2 系统整体架构

2.1 引言

2.2 系统功能及指标

2.2.1 系统功能

2.2.2 系统指标

2.3 系统硬件方案

2.4 系统FPGA固件逻辑架构设计

2.5 系统设计难点

2.5.1 FLASH阵列模块与外围模块的交互设计

2.5.2 FLASH通用控制接口设计

2.5.3 FLASH容错算法的设计及实现

2.6 本章小结

3 高速数据采集功能的设计及实现

3.1 引言

3.2 高速ADC模块设计

3.2.1 ADC芯片介绍

3.2.2 ADC芯片控制固件逻辑设计

3.3 FLASH阵列模块设计

3.3.1 FLASH芯片介绍

3.3.2 FLASH编程固件逻辑设计

3.3.3 FLASH通用控制接口设计

3.4 USB3.0上传模块设计

3.4.1 USB3.0芯片介绍

3.4.2 USB3.0固件程序及上传固件逻辑设计

3.5 采集模式FLASH阵列模块与外围模块的交互设计

3.5.1 FLASH阵列模块与高速ADC模块的交互设计

3.5.2 FLASH阵列模块与USB3.0上传模块的交互设计

3.6 本章小结

4 高速数据回放功能的设计及实现

4.1 引言

4.2 USB3.0下载模块设计

4.3 高速DAC模块设计

4.3.1 DAC芯片介绍

4.3.2 DAC芯片控制固件逻辑设计气

4.3.3 DAC时钟管理设计

4.4 回放模式FLASH阵列模块与外围模块的交互设计

4.4.1 FLASH阵列模块与USB3.0下载模块的交互设计

4.4.2 FLASH阵列模块与高速DAC模块的交互设计

4.5 本章小结

5 FLASH容错算法的设计及实现

5.1 引言

5.2 FLASH坏块管理问题描述

5.3 FLASH容错算法的设计

5.3.1 坏块检测设计

5.3.2 建立逻辑一物理地址映射表设计

5.3.3 动态更新设计

5.3.4 动态读取设计

5.4 FLASH容错算法的实现

5.4.1 坏块检测的实现

5.4.2 建立逻辑一物理地址映射表的实现

5.4.3 动态更新的实现

5.4.4 动态读取的实现

5.5 本章小结

6 系统测试

6.1 引言

6.2 系统测试方案

6.2.1 高速数据采集功能的测试方案

6.2.2 高速数据回放功能的测试方案

6.2.3 FLASH容错算法有效性测试方案

6.3 系统测试平台搭建

6.3.1 系统软件测试平台

6.3.2 系统软硬件测试平台整合

6.4 高速数据采集功能测试

6.4.1 高速ADC模块测试

6.4.2 采集模式FLASH阵列模块测试

6.4.3 USB3.0上传模块测试

6.5 高速数据回放功能测试

6.5.1 USB3.0下载模块测试

6.5.2 回放模式FLASH阵列模块测试

6.5.3 高速DAC模块测试

6.6 FLASH容错算法有效性测试

6.6.1 FLASH容错算法的实现过程测试

6.6.2 采集模式FLASH容错算法效果验证

6.6.3 回放模式FLASH容错算法效果验证

6.7 本章小结

7 总结和展望

7.1 本文小结

7.2 未来工作展望

参考文献

作者研究生期间科研成果